vlsi testing and diagnosis white papers|vlsi testing : private label Experimental results on constrained equivalence checking, enhancement of error diagnosis resolution for combinational circuits, and ATPG for IP-based designs have been presented on . web13 de set. de 2021 · TOPO DE BOLO DE SOLDADO PARA IMPRIMIR. Andre Caricaturista Instrutor de Arte. 287 subscribers. 197 views 1 year ago. Talvez você tenha alguém da família que é soldado e queira fazer a.

{plog:ftitle_list}

WEBAugust 10, 2023. By Vansh Mehra. Cars 2 is the sequel to Pixar’s original Cars movie featuring Lightning McQueen. But in the follow-up, it’s Lightning McQueen’s best friend Mater who gets .

We analyze the challenges associated with traditional VLSI testing techniques and showcase how ML algorithms are increasingly being employed to enhance fault detection, diagnosis, . Abstract: As the move to very deep submicron VLSI devices pushes the threshold of semiconductor technology, conventional test and diagnosis methods become inadequate .SPECIAL SESSION: OPERATING SYSTEMS UNDER TEST: AN OVERVIEW OF THE SIGNIFICANCE OF THE OPERATING SYSTEM IN THE RESILIENCY OF THE COMPUTING .Experimental results on constrained equivalence checking, enhancement of error diagnosis resolution for combinational circuits, and ATPG for IP-based designs have been presented on .

Several Electronic Design Automation tools for fault identification and test pattern development are available to simulate circuits for structural testing. This chapter gives a brief . The use of embedded test raises margins and significantly reduces the time required for system verification, test and debug. The paper addresses discusses embedded .

DOMAIN MEASUREMENTS...............................................7. .A Hardware-Based Evolutionary Algorithm with Multi-Objective Optimization Operators for On-. Chip Transient Fault Detection .

This is where using Machine Learning (ML) approaches for testing VLSI is useful. In this article, we'll look at how machine learning is changing VLSI testing and making failure .In this paper we address these Testing, verification, and diagnosis in the presence of unknowns . Testing, verification, and diagnosis in the presence of unknowns Abstract: . Published in: Proceedings 18th IEEE VLSI Test Symposium. Article #: Date of Conference: 30 April 2000 - . Testing verifies a circuit's accuracy regarding gates and connections between them. The fundamental purpose of testing is to model the circuit's various activities. Several Electronic Design Automation tools for fault identification and test pattern development are available to simulate circuits for structural testing.

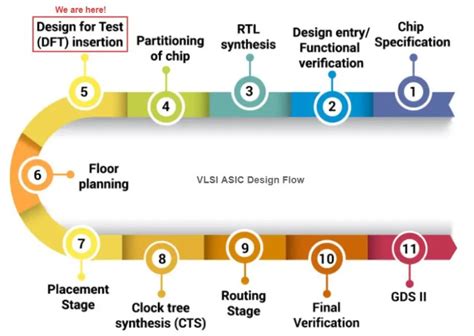

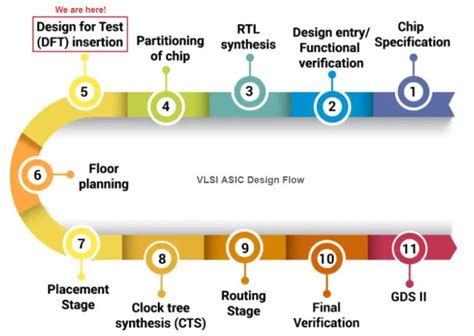

5 Books Essential of Electronic Testing for Digital, Memory, and Mixed Signal VLSI Circuits Michel.L. Bushnell and Vishwani D. Agrawal Springer 2005 Logic Testing and Design for Testability Hideo Fujiwara MIT Press 1985 Digital System Testing and Testable Design M. Abramovici, M. Breuer, A. Friedman IEEE Press 1994 (now available in Jayco Publication) VLSI Testing Trends and Advancements. As technology continues to advance, new trends and advancements in VLSI testing are emerging. Some of these include: Design for Testability (DFT) DFT is an approach that involves designing circuits with built-in testability features. These features facilitate the testing process by providing easy access to . Figure 2.3 is a simple view of how ICs will be tested. Test patterns are generated during the test development (see Fig. 2.1, where the preliminary step of testing is test development at pre-silicon), and they will be tested on the silicon after manufacturing and will be compared with the stored ones as the reference (see Fig. 2.1, where the primary step of .

VLSI Test Principles and Architectures Ch. 8-Memory Testing &BIST -P. 8 Static RAM Fault Models: SAF/TF Stuck-At Fault (SAF) Cell (line) SA0 or SA1 – A stuck-at fault (SAF) occurs when the value of a cell or line is always 0 (a stuck-at-0 fault) or always 1 (a stuck-at-1 fault). – A test that detects all SAFs guarantees that from eachVLSI Test Technology and Reliability (ET4076) 5 What is VLSI Test and reliability? • Test/Quality • Guarantee that the IC performs its function at t=0 • Conformance to specifications: time-independent • Measured in DPM (defects part per million) • Driven by defect/fault coverage & performance guard-bands • Impacts B2B relationship

Test and Diagnosis for Small-Delay Defects. Chapter. Introduction to VLSI Testing . Manage Manufacturing Test Power Issues with DFTMAX and TetraMAX”, Synopsys White Paper, 2010. Google Scholar D . B . Janusz Rajski, and Jerzy Tyszer, “Low Power Embedded Deterministic Test”, in 25th IEEE VLSI Test Symmposium (VTS’07), 2007.

ELEC7250-001 VLSI Testing (Spring 2006) Tuesday/Thursday, 11:00AM-12:15PM, Broun 235 . Wang: Paper (Random Access Scan) Report (Logic Simulation and Diagnosis) White: Paper (Boundary Scan Standard) Report (Logic Simulation and Diagnosis) LECTURES: Lecture 0: Course Organization, 1/10/06 Lecture 1: Introduction, 1/10/06 (Chapter 1)Need Help? US & Canada: +1 800 678 4333 Worldwide: +1 732 981 0060 Contact & SupportElsevier US Jobcode:0wtp-Prelims 1-6-2006 4:22p.m. Page: 5 VLSI TEST PRINCIPLES AND ARCHITECTURES DESIGN FOR TESTABILITY Edited by Laung-Terng Wang Cheng-Wen Wu Xiaoqing Wen AMSTERDAM •BOSTON HEIDELBERG LONDON NEW YORK •OXFORD PARIS SAN DIEGO SAN FRANCISCO •SINGAPORE SYDNEY • TOKYO Morgan Kaufmann .

vlsi testing technology

VLSI testing involves the following key steps: 1. Test Generation: . Diagnosis and Debugging: If faults are detected, the next step involves identifying the specific location and nature of the faults within the IC. Various diagnosis techniques, such as scan-based diagnosis, fault simulation, or logic analysis, are employed to pinpoint the .

The impact of AI on VLSI design was first demonstrated in 1985 by Robert. S. Kirk [15]. He briefly explained the scope and necessity for AI techniques in CAD tools at different levels of VLSI design. His paper included a brief on the existing VLSI–AI tools and stressed the importance of In this paper, we introduce a new fault detection model based on deep learning for extracting features and detecting faults from large-sized digital circuits. . The model consists of three phases: test pattern generation using ATALANTA software, feature reduction using SSAE and classification for fault detection. Test vectors are utilized in . This paper presents an approach to the diagnosis of linear and nonlinear analog circuits and shows that the white noise relative to the pole zero locations of the circuit transfer function has a significant impact on the classification efficiency of ANN. This paper presents an approach to the diagnosis of linear and nonlinear analog circuits. The diagnosis .

VLSI-1 Class Notes Test Pattern Generation §Manufacturing test ideally would check every node in the circuit to prove it is not stuck. §Apply the smallest sequence of test vectors necessary to prove each node is not stuck. §Good observability and controllability reduces number of test vectors required for manufacturing test.

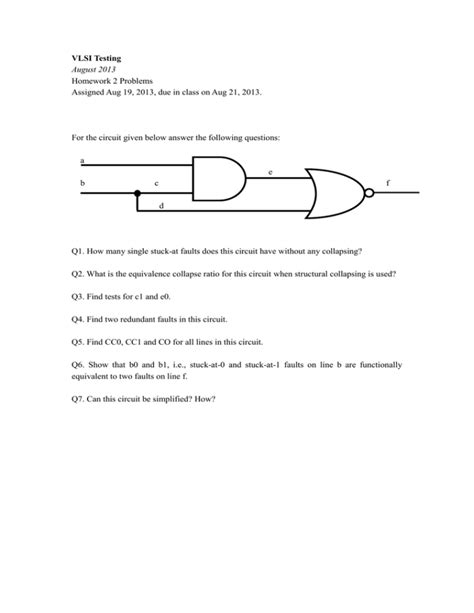

VTU MTech M.E syllabus of VLSI Testing for VLSI DESIGN AND EMBEDDED SYSTEMS First Semester 2018 scheme. . Fault Diagnosis of digital circuits, Test generation techniques for combinational circuits, Detection of multiple faults in Combinational logic circuits. . 18CS71-AiML VTU Question Papers New; Machine Learning VTU Question Papers New; Feature papers represent the most advanced research with significant potential for high impact in the field. A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications. . VLSI Design, Testing, and . Download Latest MTech VTU VLSI Testing of 1st semester VLSI DESIGN AND EMBEDDED SYSTEMS with subject code 18EVE14 2018 scheme Question Papers. . VTU VLSI Testing JAN 2020 Question Paper Download VTU 18EVE14 Jan 2020 MTech paper. Last Updated: Monday, February 13, 2023. Categories. VTU Time Table New; VTU Model .A comprehensive guide to new VLSI Testing and Design-for-Testability techniques, this text will allow you to master System-on-Chip Test architectures, and test, debug, and diagnose digital, memory, and analog/mixed-signal designs. . These design features are generally referred to as design for debug and diagnosis (DFD). We explain how these .

This document, White Paper 4, (WP) has been carefully compiled by the Industry Council on ESD Target Levels to foster a unified global understanding of what constitutes EOS and how EOS damage signatures can result from a wide variety of root causes. The paper begins by outlining a brief history of EOS.Testing and Diagnosis of VLSI and ULSI" held at Villa Olmo, Como (Italy) June 22 -July 3,1987. High Density technologies such as Very-Large Scale Integration (VLSI), Wafer Scale Integration (WSI) and the not-so-far promises of Ultra-Large Scale .

His research interests include Digital Design, Embedded Systems, System-on-Chip (SoC) and Network-on-Chip (NoC) Design and Test, Power- and Thermal-aware Testing of VLSI Circuits and Systems. He has published more than 150 papers .

The impact of AI on VLSI design was first demonstrated in 1985 by Robert. S. Kirk [15]. He briefly explained the scope and necessity for AI techniques in CAD tools at different levels of VLSI design. His paper included a brief on the existing VLSI–AI tools and stressed the importance of incorporating the expanded capabilities of AI in CAD tools.DFTS 2024 Special Issue in Microprocessors and Microsystems (MICPRO) journal Defect and fault tolerance in VLSI and nanotechnology systems including emerging technologies, RISC-V architectures and AI-based solutions, are pervasive topics spanning domains and applications.

vlsi testing problems

This paper first reviews the basics of VLSI testing, focusing on test generation and design for testability. Then it discusses the impact of test power in scan testing, and highlights the need for low-power VLSI testing.

This set of VLSI Multiple Choice Questions & Answers (MCQs) focuses on “Test and Testability “. 1. Circuit nodes cannot be probed for monitoring or excitation. a) true . The stuck at model is used in the testing of pc boards and is not sufficient to test actual VLSI CMOS circuits. Sanfoundry Global Education & Learning Series – VLSI.

$40.00

vlsi testing and diagnosis white papers|vlsi testing